# El inversor CMOS y su uso en el diseño de sistemas de mayor complejidad

F. Sandoval-Ibarra

Diseño Electrónico, CINVESTAV-Guadalajara, Prol. Av. López-Mateos Sur 590, 45235 Guadalajara, Jalisco (México)

#### E. Montoya-Suárez

Fac. de Ciencias e Ingenierías, Universidad Autónoma de Nayarit, Cd. de la Cultura Amado Nervo, Tepic, Nayarit (México)

Recibido el 24 de noviembre de 2003; aceptado el 22 de enero de 2004

En este artículo se presenta el diseño de sistemas digitales a partir del uso de un circuito inversor básico, denominado de aquí en adelante *celda básica*. El propósito no solo es mostrar la utilidad de la celda en el diseño de sistemas de mayor complejidad sino también mostrar las consideraciones de diseño y de pruebas útiles en el proceso de caracterización de los sistemas bajo análisis. Los circuitos mostrados fueron fabricados en una tecnología CMOS,  $1.2\mu m$ , pozo N.

Descriptores: Tecnología CMOS; circuitos digitales; layout.

This paper presents the design of digital systems by using a basic inverter circuit, hereafter named *basic cell*. The purpose of this work is not only to show the usefulness of this cell to design major systems, but also to depict design considerations, as well as test hints for the characterization process of the systems under analysis. All circuits were manufactured in a CMOS technology,  $1.2\mu m$ , N-well.

Keywords: CMOS technology; digital design; layout.

## 1. Introducción

En la actualidad, el diseño físico es una actividad que ha evolucionado a la par de la tecnología de fabricación de circuitos integrados. En el pasado reciente, el diseño de circuitos en tecnología MOS no consideraba diversas no-idealidades debido al uso de transistores de gran canal, es decir, mucha de la tarea del diseñador consistía en el diseño denominado top-down y, en muy pocas situaciones, se involucraba en el diseño a nivel transistor. La razón es simple, los modelos simplificados o aproximados en programas de simulación de circuitos de propósitos generales, como SPICE, reproducían bien el desempeño de los circuitos y/o sistemas. Con la evolución de la tecnología, diversos factores físicos ahora están presentes y el desarrollo de modelos compactos de alta confiabilidad es una necesidad. Sin embargo, si bien es cierto que no hay una tradición en México relacionada con el diseño de circuitos integrados a nivel licenciatura, también es cierto que esa cultura se debe generar y para ello, es propósito del presente documento mostrar la utilidad que el circuito inversor tiene en el diseño de sistemas digitales de mayor complejidad. Conforme ésta aumenta, los modelos matemáticos usados para el diseño de tales sistemas deben ser modificados no solo para corroborar el desempeño del sistema, sino también para optimizarlo. En la práctica, tanto el modelado del transistor MOS como el desarrollo de modelos matemáticos constituyen enormes campos de aplicación, los cuales no serán descritos en este documento por cuestiones de espacio. Pero, sí se mostrará una metodología simple que permita observar cómo a partir de una celda básica, de naturaleza digital, es posible incrementar las funciones de un circuito. Estos circuitos, están necesariamente incluidos en todo sistema de señal mezclada, es decir, en aquellos desarrollos compuestos de circuitería analógica y mayoritariamente digital.

## 2. El oscilador de anillo

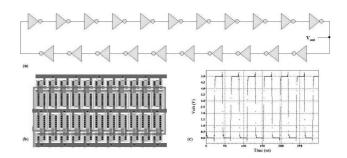

El desempeño en el dominio del tiempo de un circuito inversor es función de dos parámetros fundamentales denominados tiempo de carga y tiempo de descarga. Manteniendo control de estos parámetros el diseño de un oscilador de anillo (OA) es inmediato. En la actualidad, un OA se usa para diversos propósitos, por ejemplo, para evaluar y/o monitorear variaciones en los procesos de fabricación [1] y, básicamente, en aquellas aplicaciones en las que se requiera una fuente generadora de pulsos de reloj. En la práctica, el OA más simple se obtiene conectando en serie un número impar de inversores, en el que el nodo de salida del último inversor es conectado al nodo de entrada del primero (ver Fig. 1a). Este arreglo particular puede ser considerado una red de comunicación de un solo sentido, en la que la señal generada por un inversor es la señal excitadora del siguiente inversor y así sucesivamente.

FIGURA 1. Arquitectura de un OA simple (a). El *layout* resultante se realiza a partir de una celda básica con lo cual se obtiene un diseño regular y compacto (b). La señal, resultado de simulación, se le denotará como  $\Phi$  (c).

Hoy en día el uso del inversor CMOS es práctica común en diversas áreas del conocimiento, sin embargo, poca gente sabe que este circuito fue inventado por Frank Wanlass, quién en febrero de 1991 recibió el denominado *IEEE Solid-State Circuits Award* [2]. La importancia del inversor CMOS radica en su bajo consumo de potencia, el cual en la década de los 60 se redujo, respecto a los circuitos bipolares de aquella epoca, en 6 órdenes de magnitud. Por lo tanto, cuando se usa este circuito el interés principal radica en su desempeño lógico y no tanto en su consumo de potencia[En tecnologías submicrométricas la densidad de integración es tan alta que el mínimo consumo de potencia es una especificación del diseño].

Por lo tanto, para cada par de inversores (i y j) conectados en serie es posible que i reciba una señal lógica denotada por "1" y cuando éste genera una respuesta que es enviada a j, la señal generada por este último será necesariamente un "1". Por lo cual se puede concluir que esta red envía un "0" de i a j. Adicionalmente, considerando que un OA es un sistema inestable no es posible diseñarlo con un número par de inversores, ya que este hecho lo haría un sistema estable, en otras palabras, la inestabilidad es el causante de su característica oscilatoria. Una desventaja de esta clase de OA es que su frecuencia de oscilación es completamente dependiente del retardo intrínseco del inversor, por lo que la frecuencia de oscilación no puede ser controlada por medios externos. En la práctica, a partir del diseño a nivel *layout* no sólo se puede estimar el valor de las capacitancias parásitas propias del transistor MOS, sino también es posible determinar la parásita debida a las líneas de polisilicio, las cuales son usadas para propósitos de interconexión. La existencia de tales parásitas dan lugar a cuantificar los tiempos en que éstas se cargan o descargan a determinado potencial. Por ejemplo, en tecnologías VLSI (del inglés <u>Very Large Scale of Integration</u>) CMOS, pozo N,  $1.2\mu m$ , la capacitancia de entrada para un inversor puede ser del orden de 3fF. Aun cuando ésta sea muy pequeña, ella permite la oscilación de la red. El oscilador mostrado en la Fig. 1b está compuesto de 21 inversores y para verificar su periodo de oscilación se usó Tspice [3]. La simulación mostró que el OA tiene una frecuencia de aproximadamente 23MHz (ver Fig. 1c). Como se puede ver de la Fig. 1b, el OA se diseñó a partir de una celda básica que fue diseñada para que la interconexión entre celdas fuera fácil, con lo cual se optimiza el área de integración.

#### 2.1. El Inversor CMOS

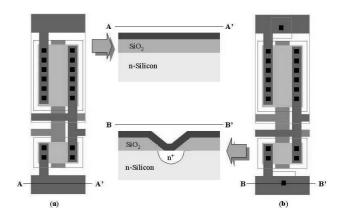

La Fig. 2 muestra el patrón geométrico del inversor básico para desarrollar diseño digital con alineación horizontal. Esta celda conduce una corriente  $I_{BIAS}$ , sin embargo, cuando se requiere un mayor manejo de corriente, el diseño de la celda permite la conexión fácil de celdas idénticas y obtener una corriente  $\mathbf{m}I_{BIAS}$ , donde  $\mathbf{m}$  representa el número de celdas conectadas en paralelo. Por ejemplo, si se consideran las celdas mostradas en la Fig. 2 y se hace un acercamiento entre ellas, se puede ver que éstas se conectan directamen-

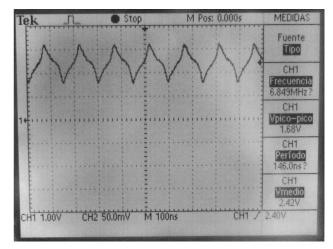

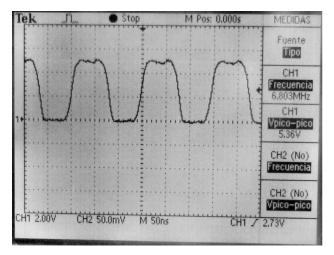

te mediante líneas de polisilicio y de metal. Por lo tanto, no es necesario generar un contacto adicional entre celdas. Este procedimiento también ocurre en las líneas a través de las cuales se alimenta cada una de las celdas. Para este ejemplo, el circuito conducirá una corriente 2I<sub>BIAS</sub>. El OA mostrado en la Fig. 1b fue fabricado y caracterizado usando una alimentación V<sub>DD</sub>=5V; el resultado obtenido se muestra en la Fig. 3, donde, como se puede observar, la respuesta (6.8MHz) es diferente a la obtenida de simulación. La respuesta del OA fue capturada con un osciloscopio Tektronix TDS210, el cual presenta una capacitancia de 13.3pF. Del punto de vista físico, la carga capacitiva de la punta de medición es la responsable del desempeño anómalo del OA, ya que los tiempos de carga y descarga son diferentes de los tiempos obtenidos de simulación. En la práctica no sólo es importante la carga capacitiva de la punta del osciloscopio sino también la debida a pads y a las pistas conductoras usadas para conexiones internas del circuito integrado. En diseños de alta densidad de integración en el que las líneas de alimentación son de longitud considerable, ya no se puede omitir ni la resistencia ni su naturaleza capacitiva con el substrato semiconductor. Por lo que un modelo RC puede ser usado para considerar el efecto de línea de transmisión resultante.

FIGURA 2. Inversor CMOS sin conexión a substrato (a). Cuando el contacto a substrato es incluido se minimizan efectos parásitos (b).

FIGURA 3. Respuesta del OA formado por 21 inversores complementarios.

# 3. Manejo de cargas capacitivas grandes

La respuesta experimental presenta tiempos de carga y descarga grandes, de manera que es fundamental considerar un circuito que permita la recuperación de  $\Phi$  sin que ello implique un consumo importante de potencia. Los efectos capacitivos que dieron lugar a la señal mostrada en la Fig. 3 pueden ser atribuidos a una carga equivalente  $C_L$ , por lo tanto, si ésta es de un gran valor es fundamental que la señal  $\Phi$  sea capaz de cargar dicha capacitancia, en un tiempo  $\Delta t$ , al menos al 95 % del valor de  $V_{DD}$ . A ese potencial se le denotará simplemente  $\Delta V$ . La solución natural a ese requerimiento es un circuito compuesto de dos inversores conectados en serie. En diseño de sistemas digitales, los circuitos responsables del manejo de cargas capacitivas grandes se les denomina buffer. Este circuito es sencillo y no contribuye al consumo de potencia, excepto la debida a la corriente de corto-circuito  $I_{meas}$ . Sin embargo, esta solución es aplicable sólo si el manejo de una carga capacitiva grande no requiere de una operación a alta frecuencia, ya que la respuesta del circuito será en consecuencia lenta. Por lo tanto, para mejorar el desempeño del  $buffer^2$  es recomendable incrementar el número de inversores. En la práctica, la cantidad necesaria de inversores se obtiene al minimizar el retardo de la señal generado por la carga  $C_L$ , el cual está dado por

$$t_D = C_L \cdot \frac{\Delta V}{I_{meas}}.\tag{1}$$

De (1) se puede concluir que incrementando  $I_{meas}$  el retardo se minimiza, equivalentemente el mismo efecto ocurre aumentando la geometría de los transistores del inversor. Aún más, existe un procedimiento en el que aumentando gradualmente la geometría de cada uno de los inversores, el último es de tal dimensión que tiene la capacidad de manejar grandes cargas capacitivas, con una característica adicional: su retardo será el dominante en toda la cadena de inversores que componen al *buffer*. Por lo tanto, para el manejo de  $C_L$  ¿cuántos inversores deben ser dimensionados de modo que el retardo  $t_D$  sea mínimo?

#### 3.1. Diseño del buffer simple

Suponer que se tiene una cadena de  ${\bf n}$  inversores conectados en serie escalados por un parámetro  ${\bf a}$  que permite minimizar  ${\bf t}_D$ . Este buffer, mostrado en la Fig. 4, presenta una capacitancia  ${\bf C}_k$  (donde  ${\bf k}{=}1,\,2,\,\ldots{\bf n}$ ) que es el resultado de varias contribuciones. Una de ellas es la capacitancia debida a los drenajes de los transistores que forman el inversor, es decir, es una capacitancia de salida. Mientras que otra contribución es originada por la conexión de compuerta de ambos transistores a un nodo común, en otras palabras, es la capacitancia de entrada del siguiente inversor  $({\bf C}_{k+1})$ . Por lo tanto, la capacitancia de drenaje y compuerta del k-ésimo inversor pueden definirse por  ${\bf a}^k{\bf C}_g$  y  ${\bf a}^k{\bf C}_d$ , respectivamente. En consecuencia, es fácil mostrar que  ${\bf C}_k{=}{\bf a}^k{\bf C}_d{+}{\bf a}^{k+1}{\bf C}_g$ . De acuerdo

a este procedimiento la capacitancia de carga estará dada por

$$C_L = a^{n+1} \cdot C_q. (2)$$

Luego, si se requiere que el retardo de cada inversor sea de igual magnitud, el retardo total puede representarse mediante el siguiente modelo [4]

$$t_{total} = (n+1) \cdot t_D \cdot \frac{C_d + a \cdot C_g}{C_d + C_g}.$$

(3)

Para determinar el valor necesario de inversores es condición suficiente despejar ese parámetro de (2). Si bien es cierto que ese resultado es función únicamente de  $\bf a$ , también es cierto que al sustituirlo en (3) resulta una expresión para  $\bf t_{total}$ , la cual deberá ser minimizada ( $\bf dt_{total}/\bf da=0$ ) y de ese procedimiento se obtiene el valor óptimo de  $\bf a$  y en consecuencia el correspondiente a  $\bf n$ . Se invita al lector demostrar que la ecuación resultante está dada por

$$a \cdot [\ln(a) - 1] = \frac{C_d}{C_q}.$$

(4)

Un caso especial resulta cuando se satisface la relación  $C_d \ll C_q$ , con lo cual el resultado es **a**=e=2.718. Considerando el diseño de inversor mostrado anteriormente, se tiene una razón capacitiva de 319×10<sup>-3</sup>, con lo cual el factor de escalamiento es el mencionado líneas arriba. A manera de ejemplo, suponer que para una carga particular C'<sub>L</sub> la cantidad de inversores del buffer requerido es **n**=2. Independientemente de la geometría del primer inversor, el segundo tendrá una geometría 2.718 más grande que el primero, es decir, si el ancho del transistor NMOS del primer inversor es  $W_1$ , el ancho del transistor NMOS del segundo inversor será necesariamente  $W_2=2.718W_1$ . Si hubiera necesidad de un tercer inversor la geometría sería  $W_3=(2.718)^2W_1=7.387W_1$ . Como se puede observar, no resulta práctico diseñar cada uno de los inversores del buffer, sobretodo cuando el número de inversores es muy alto. Por lo tanto, si el primer inversor es la celda básica mostrada en la Fig. 2, el segundo pudiera ser el formado por la conexión en paralelo de 3 celdas básicas, mientras que el tercer inversor puede ser la conexión en paralelo de 7 u 8 celdas. Es decir, a partir de una sola celda es posible diseñar el buffer requerido. La Tabla I muestra la cantidad de inversores escalados necesarios para manejar una carga  $C_L$ , e indica la cantidad de celdas básicas para su implementación. Los datos que se proporcionan son para la celda básica mostrada en la Fig. 2 y para la tecnología descrita.

FIGURA 4. Un *buffer* consiste de una cadena de n inversores, donde  $C_1=C_d+\mathbf{a}C_g$ ,  $C_2=\mathbf{a}(C_d+\mathbf{a}C_g)$ ,  $C_3=\mathbf{a}^2(C_d+\mathbf{a}C_g)$ , y así sucesivamente.

Tabla I. Número de inversores y celdas básicas para manejar una carga  $\mathbf{C}_L$ .

| $C_L(pF)$ | n | Inverters |

|-----------|---|-----------|

| 1-2       | 2 | 12        |

| 3-7       | 3 | 39        |

| 8-19      | 4 | 120       |

| 20        | 5 | 363       |

#### 3.2. Diseño a nivel layout

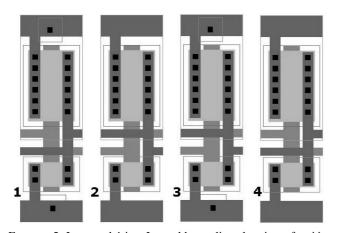

El uso de una celda básica permite el diseño regular y compacto del buffer a implementar. Por lo anterior, y solo para propósitos de ilustración, el factor de escalamiento es un número entero, es decir el valor obtenido para a fue redondeado a 3. El diseño de la celda básica, de arriba a abajo, está compuesta por un transistor canal P y otro de canal N, además, una de las celdas tiene conexión a substrato y la otra celda no la tiene. La ventaja de contar con este par de celdas básicas es que cualquiera de ellas puede ser girada respecto a la horizontal de modo que ambas coincidan ya sea en la pista de  $V_{DD}$  o bien la de  $V_{SS}$ . El resultado de esta conexión es que ambas celdas tienen contacto a substrato y evita que el diseño del buffer se realice en un único y largo renglón de celdas. Para la descripción realizada, el diseño ocupa ahora dos renglones. Cabe recordar que estas celdas básicas se diseñaron para la conexión fácil entre ellas en paralelo, pero un contacto adicional deberá ser realizado para la conexión entre los inversores escalados que forman el buffer. Esta conexión deberá realizarse sin que ello implique área adicional y/o evitar en lo posible alterar la regularidad del diseño. En la práctica esas precauciones pueden ser omitidas mediante la modificación de las celdas dadas en la Fig. 2, el conjunto de celdas básicas se muestra en la Fig. 5.

Se puede observar que el acercamiento entre las celdas 2 y 3 no genera una conexión física, sin embargo, este acercamiento permite generar un contacto polisilicio-metal sin que ello implique área adicional y trabajo extra para el diseñador.

FIGURA 5. Inversor básico. Las celdas realizan la misma función excepto que se diseñan para fácil conexión en paralelo (1,2,4) y para la conexión serie que se requiera (2,3).

FIGURA 6. Asumiendo una carga de 15pF, y **a**=3 se requieren 120 celdas básicas para construir un buffer de 4 inversores escalados (a). La estrategia de diseño se muestra en (b).

Por ejemplo, para manejar una carga de 15pF (ver Fig. 6a) se requieren cuatro inversores escalados (120 celdas básicas), los cuales pueden ser ordenados de acuerdo a la estrategia de diseño que se muestra en la Fig. 6b, donde 3 renglones de celdas son suficientes para diseñar el *buffer*. El área de integración resultante es  $564 \times 127 \mu m^2$ .

## 3.3. Resultado experimental

La fabricación del OA y del *buffer* se realizó de acuerdo a las reglas de diseño de la tecnología  $1.2\mu m$ , CMOS, pozo N. La respuesta experimental se muestra en la Fig. 7, donde la frecuencia de oscilación es de 6.8 MHz. A diferencia de la respuesta mostrada en la Fig. 3 el *buffer* permite en un tiempo muy corto la carga y descarga de  $C_L$ .

El desempeño del *buffer* es para una carga cuyo valor satisface la siguiente relación  $15.5 \mathrm{pF} < C_L < 19 \mathrm{pF}$ . Se puede apreciar que la respuesta es bien definida, sin embargo, aún cuando el *buffer* realiza su función, éste ocupa una área de integración importante. Por tal razón es recomendable no hacer un redondeo del factor de ajuste, en tal caso, considerando que  $\mathbf{a} = 2.718$ , la cantidad de celdas requeridas es de solo 83. Reducir el diseño en 37 celdas implica, además de minimizar área de integración, reducir el consumo de potencia.

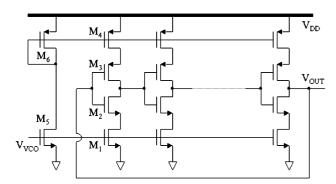

# 4. Inversor CMOS modificado

La Fig. 8 muestra un OA con control de la frecuencia de oscilación. Los transistores  $M_2$  y  $M_3$  forman el inversor básico, mientras que  $M_1$  y  $M_4$  operan como fuentes de corriente. Estos últimos controlan la corriente que fluye por el inversor, con lo cual éste se ve forzado a operar con ese flujo de corriente. Estrictamente hablando, controlar el flujo de corriente representa tener control de los tiempos de carga y descarga o, lo que es lo mismo, tener control de la frecuencia de oscilación,  $f_{osc}$ .

FIGURA 7. Respuesta del OA formado por 21 inversores complementarios y un buffer de salida. La carga debida a la punta del osciloscopio y pads es del orden de 15pF.

FIGURA 8. Topología a nivel transistor del OA formado por 9 inversores (controlados por corriente). En esta representación  $V_{VCO}$  es el voltaje de control.

El transistor  $M_5$  es una fuente de corriente controlada por el voltaje  $V_{VCO}$ . La corriente que fluye por  $M_6$  es reflejada por  $M_4$ , ya que ellos constituyen un espejo de corriente básico. Como es de suponer, la rama de corriente  $M_1$ - $M_4$  es un inversor controlado por corriente y éste es el arreglo que se dispone en serie tantas veces como sea necesario para formar el lazo de oscilación. Los detalles de este diseño se pueden consultar en la Ref. 5, aquí sólo se mencionará que para un OA de N inversores ( $N \ge 3$ ) la frecuencia de oscilación se puede aproximar mediante el siguiente modelo:

$$f_{osc} = \frac{\xi \cdot I_{BIAS}}{N \cdot C_{tot} \cdot V_{DD}},\tag{5}$$

donde  $C_{tot}$  representa la capacitancia total en el nodo común a los drenajes de  $M_2$  y  $M_3$ . Mientras que  $\xi$  es un parámetro de ajuste propio de la tecnología.

En este modelo se asume que  $M_5$  opera en su región de saturación, con lo que el OA abandonará su estado de oscilación para voltajes de control dados por  $(V_{VCO}-V_{Tn}) < V_{DSAT}$ , siendo  $V_{Tn}$  y  $V_{DSAT}$  los voltajes de encendido y de saturación del transistor  $M_5$ , respectivamente. Para analizar este OA se implementó un diseño

formado por 9 inversores controlados por corriente. Para observar el comportamiento de este circuito a diferentes tipos de señales de control  $V_{VCO}$ , se aplicó una rampa de voltaje en el nodo de control, observando que a mayor voltaje de control menor duración del ancho del pulso, y a menor voltaje de control menor frecuencia de oscilación. A manera de ejemplo, en la Fig. 9a se muestra el comportamiento del OA aplicando una polarización de 5 V. Sin embargo, para una adecuada vizualización del desempeño del OA, es conveniente analizar la curva  $V_{VCO}$  vs.  $f_{osc}$  mostrada en la Fig. 9b. En la práctica, la pequeña desviación experimental que se observa es información que da lugar a la cuantificación de  $\xi$ , este último es un factor de ajuste. En este experimento la frecuencia de oscilación está centrada en 204.8 kHz con un voltaje de control de 2.74 V.

Considerando la región lineal de la curva, se obtiene un modelo aproximado de la frecuencia de oscilación dado por

$$f_{osc} \approx 232.04 \times 10^3 \cdot (V_{VCO} - 1.58),$$

(6)

donde  $[f_{osc}]$ =Hz, con un coeficiente de correlación lineal de 0.999, y un intervalo de validez limitado por la desigual-dad  $2.2 \text{V} \leq \text{V}_{VCO} \leq 4 \text{V}$ . Obsérvese que para tener control de la frecuencia de oscilación este diseño incorpora espejos de corriente, es decir, circuitos de uso común en diseño analógico. No es ésta la única opción para tener control de la frecuencia de oscilación, sin embargo, el propósito es mostrar la capacidad de control sobre  $f_{osc}$ .

FIGURA 9. Funcionamiento del VCO: Respuesta a una rampa de voltaje (a).  $f_{osc}$  vs.  $V_{VCO}$  (b).

#### 5. Conclusiones

El circuito inversor CMOS mostrado en este documento fue inventado y patentado (No. de registro 3,356,858) por Frank Wanlass el 5 de diciembre de 1967. Este circuito no sólo fue el progenitor de todos los circuitos integrados de la actualidad, también fue y sigue siendo la base para el diseño de sistemas de mayor complejidad, del cual el OA es sólo un ejemplo. Los circuitos osciladores mostrados en este documento han sido desarrollos generados tanto en el aula como en trabajos de tesis. Finalmente, es importante mencionar que estos diseños incluyen el desarrollo de técnicas a nivel *layout* para el diseño compacto de las celdas y, al mismo tiempo, optimizar área de integración. Por lo tanto, el uso de software

profesional es básico en esta clase de diseños. Por otro lado, para propósitos académicos es posible acudir a las empresas que desarrollan esta clase de software y adquirir éste en su modalidad licencia académica. Alternativamente, es posible acudir al portal correspondiente y descargar el software demostrativo, el cual está disponible a todo público [6]. Seguramente tendrá limitaciones, sin embargo, permitirá introducirse en esta clase de diseño.

# **Agradecimientos**

El chip de prueba fue fabricado bajo el auspicio del Programa Académico MOSIS. Este trabajo se realizó con financiamiento del CONACyT-México (convenio 38951-A).

- S. Fuentes-Goiz, Determinación de Funcionalidad de Circuitos Integrados Digitales CMOS, Tesis Maestría, INAOE, Puebla (México), 1990

- 2. Michael J. Riezenman, IEEE SPECTRUM (1991) 44.

- 3. Tspice, User manual (Tanner Research Inc, 1997).

- M. Shoji, CMOS Digital Circuit Technology (Prentice Hall, New Jersey, 1988).

- E. Montoya-Suárez, Diseño y Fabricación de Bloques Básicos para la Construcción de un DPLL, Tesis Maestría, CINVESTAV-Guadalajara (2002).

- La liga (www.tanner.com/EDA/) proporciona software demostrativo para simulación de circuitos a nivel transistor y, además, para el diseño a nivel layout

- Una versión demostrativa de Pspice se puede obtener en www.microsim.com/